BSPIO-OPTO1212-DS0 pages

Digital Modules for Boundary

Scan Parallel I/O Access

Via Rocca di Papa, 21 –00179 Roma, Italy

Email: info@geb-enterprise.com - Web: www.geb-enterprise.com

Model: BSPIO-OPTO1212

Features

•

•

•

•

•

•

•

•

•

•

•

•

12 Optoisolated input channels

12 Optoisolated output channels

High reliabilty DIN41612 I/O connector

Reliable screw lock brackets

Size 122mm X 70mm

I/O organized in 1 segment

96 bit Boundary-scan Register Length

Each segment can be independently bypassed

Medium-speed 10MHz TCK for high reliability at the best cost/performance ratio

Fully-compatible JTAG/IEEE 1149.1 Test Access Port (TAP)

Operating power 3.3V, 5.0V

Optional LVDS TCK interface can be used in large fixtures to avoid noise and skew problems.

General Description

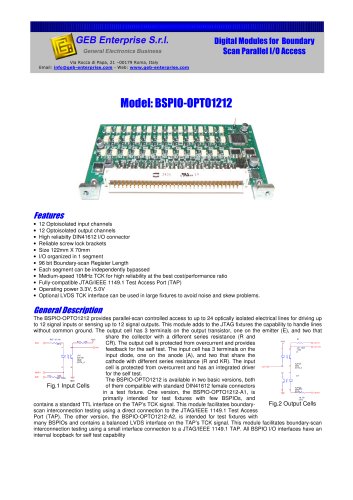

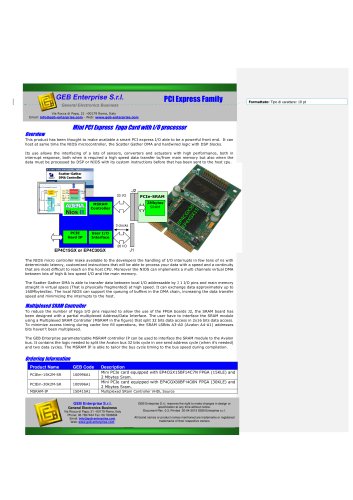

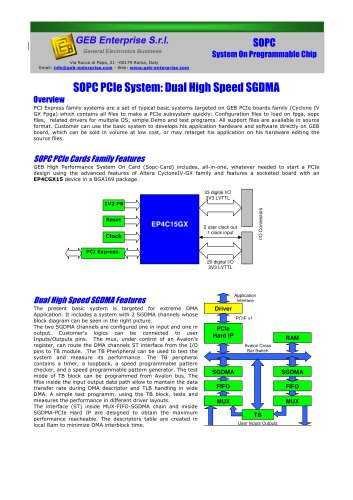

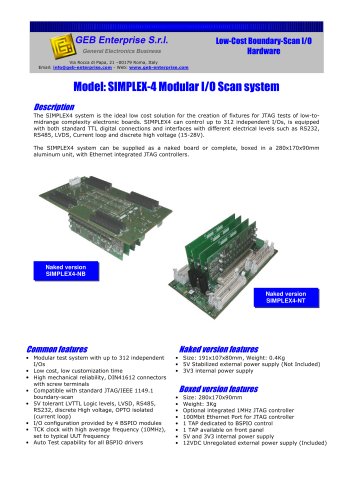

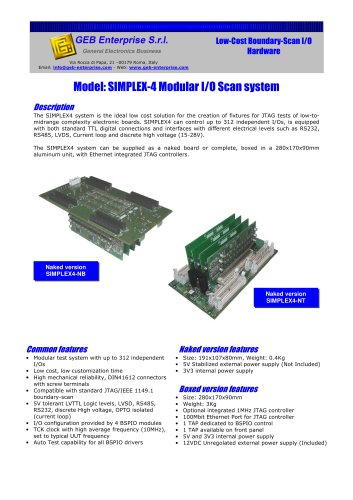

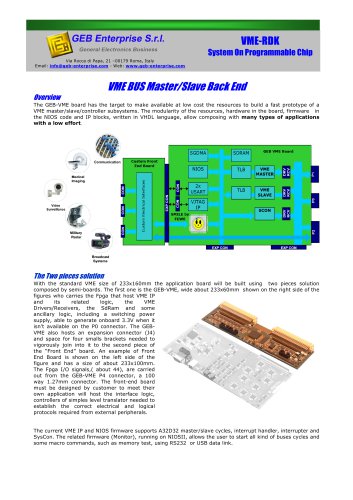

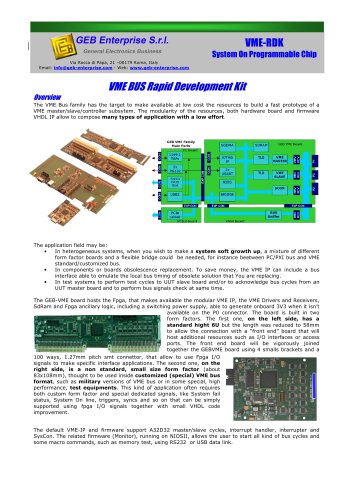

The BSPIO-OPTO1212 provides parallel-scan controlled access to up to 24 optically isolated electrical lines for driving up

to 12 signal inputs or sensing up to 12 signal outputs. This module adds to the JTAG fixtures the capability to handle lines

without common ground. The output cell has 3 terminals on the output transistor, one on the emitter (E), and two that

share the collector with a different series resistance (R and

CR). The output cell is protected from overcurrent and provides

feedback for the self test. The input cell has 3 terminals on the

input diode, one on the anode (A), and two that share the

cathode with different series resistance (R and KR). The input

cell is protected from overcurrent and has an integrated driver

for the self test.

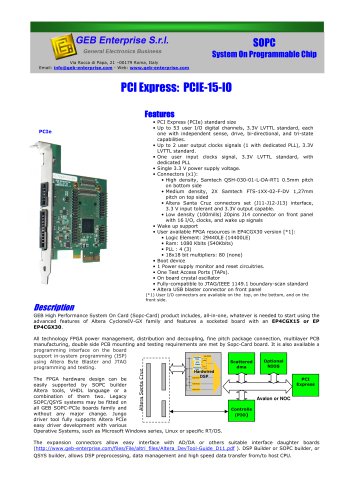

The BSPIO-OPTO1212 is available in two basic versions, both

Fig.1 Input Cells

of them compatible with standard DIN41612 female connectors

in a test fixture. One version, the BSPIO-OPTO1212-A1, is

primarily intended for test fixtures with few BSPIOs, and

Fig.2 Output Cells

contains a standard TTL interface on the TAP’s TCK signal. This module facilitates boundaryscan interconnection testing using a direct connection to the JTAG/IEEE 1149.1 Test Access

Port (TAP). The other version, the BSPIO-OPTO1212-A2, is intended for test fixtures with

many BSPIOs and contains a balanced LVDS interface on the TAP’s TCK signal. This module facilitates boundary-scan

interconnection testing using a small interface connection to a JTAG/IEEE 1149.1 TAP. All BSPIO I/O interfaces have an

internal loopback for self test capability

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید