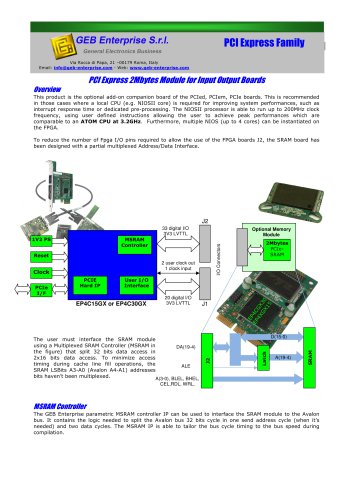

PCIe Standard PC CARD0 pages

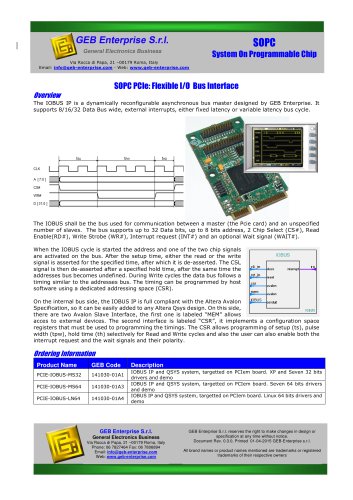

SOPC

System On Programmable Chip

Via Rocca di Papa, 21 –00179 Roma, Italy

Email: info@geb-enterprise.com - Web: www.geb-enterprise.com

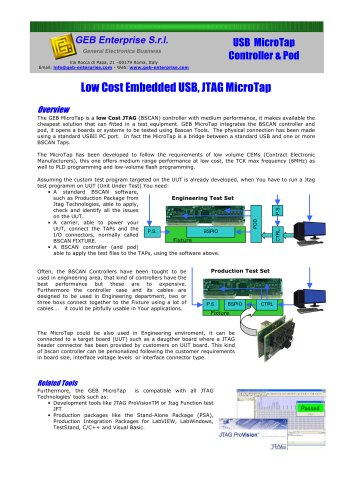

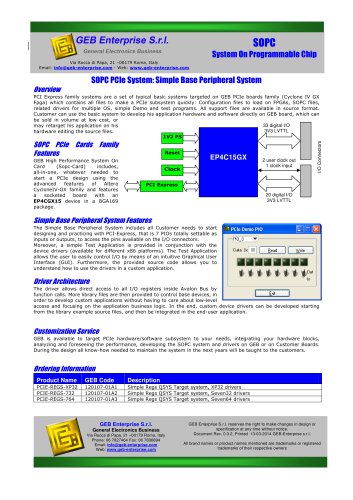

PCI Express: PCIE-15-IO

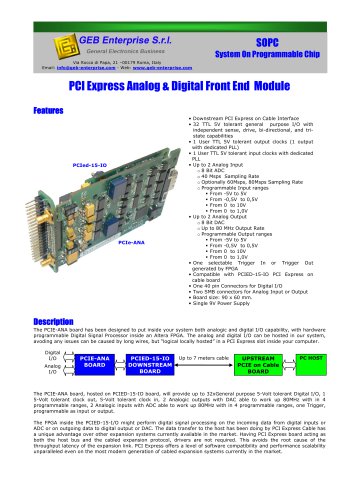

Features

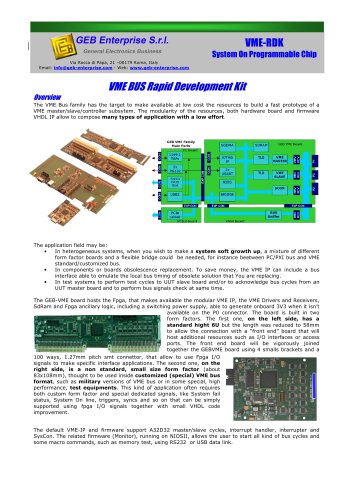

• PCI Express (PCIe) standard size

• Up to 53 user I/O digital channels, 3.3V LVTTL standard, each

one with independent sense, drive, bi-directional, and tri-state

capabilities.

• Up to 2 user output clocks signals (1 with dedicated PLL), 3.3V

LVTTL standard.

• One user input clocks signal, 3.3V LVTTL standard, with

dedicated PLL

• Single 3.3 V power supply voltage.

• Connectors (x1):

• High density, Samtech QSH-030-01-L-DA-RT1 0.5mm pitch

on bottom side

• Medium density, 2X Samtech FTS-1XX-02-F-DV 1,27mm

pitch on top sided

• Altera Santa Cruz connectors set (J11-J12-J13) interface,

3.3 V input tolerant and 3.3V output capable.

• Low density (100mills) 20pins J14 connector on front panel

with 16 I/O, clocks, and wake up signals

• Wake up support

• User available FPGA resources in EP4CGX30 version [*1]:

• Logic Element: 29440LE (14400LE)

• Ram: 1080 Kbits (540Kbits)

• PLL : 4 (3)

• 18x18 bit multipliers: 80 (none)

• Boot device

• 1 Power supply monitor and reset circuitries.

• One Test Access Ports (TAPs).

• On board crystal oscillator

• Fully-compatible to JTAG/IEEE 1149.1 boundary-scan standard

• Altera USB blaster connector on front panel

PCIe

(*1) User I/O connectors are available on the top, on the bottom, and on the

front side.

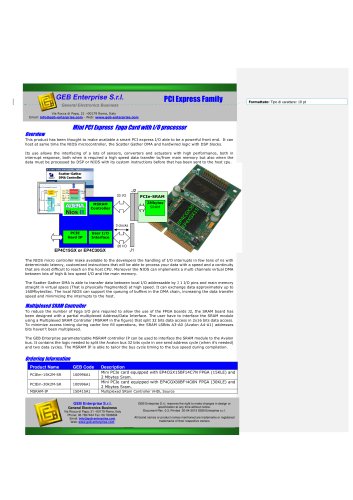

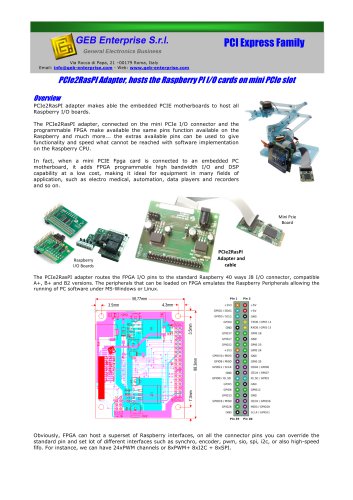

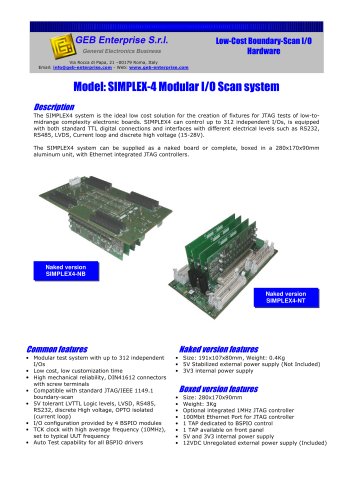

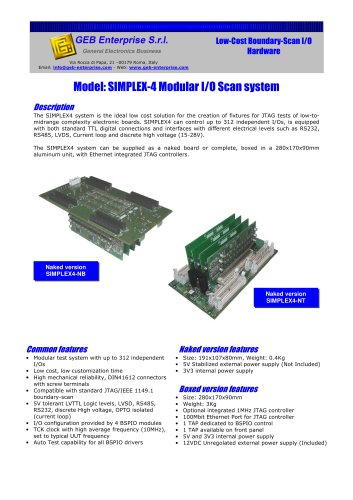

Description

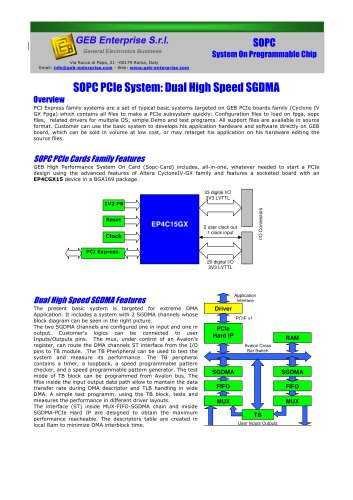

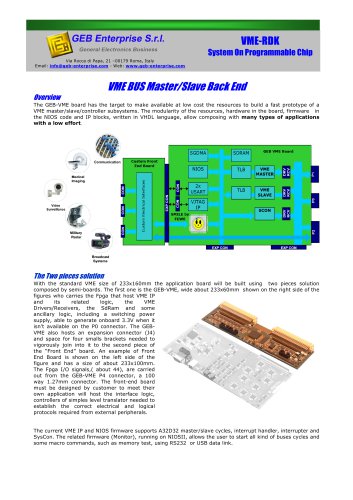

GEB High Performance System On Card (Sopc-Card) product includes, all-in-one, whatever is needed to start using the

advanced features of Altera CycloneIV-GX family and features a socketed board with an EP4CGX15 or EP

EP4CGX30.

Altera Santa Cruz

All technology FPGA power management, distribution and decoupling, fine pitch package connection, multilayer PCB

manufacturing, double side PCB mounting and testing requirements are met by Sopc-Card board. It is also available a

programming interface on the board

support in-system programming (ISP)

Optional

Scattered

using Altera Byte Blaster and JTAG

NIOS

dma

programming and testing.

Hardwired

DSP

The FPGA hardware design can be

easily supported by SOPC builder

Altera tools, VHDL language or a

combination of them two. Legacy

SOPC/QSYS systems may be fitted on

all GEB SOPC-PCIe boards family and

without any major change. Jungo

driver tool fully supports Altera PCIe

easy driver development with various

Operative Systems, such as Microsoft Windows series, Linux or specific RT/OS.

PCI

Express

Avalon or NOC

Controlls

(PIO)

The expansion connectors allow easy interface with AD/DA or others suitable interface daughter boards

(http://www.geb-enterprise.com/files/File/altri_files/Altera_DevTool-Guide_D11.pdf ). DSP Builder or SOPC builder, or

QSYS builder, allows DSP preprocessing, data management and high speed data transfer from/to host CPU.

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید