ADSP-CM402F/CM403F/CM407F/CM408F/CM409F: Mixed-Signal Control Processor with ARM Cortex-M4 and 16-bit ADCs0 pages

Mixed-Signal Control Processor

with ARM Cortex-M4 and 16-Bit ADCs

ADSP-CM402F/CM403F/CM407F/CM408F/CM409F

SYSTEM FEATURES

Full Speed USB on-the-go (OTG)

Two CAN (controller area network) 2.0B interfaces

Three UART ports

Two serial peripheral interface (SPI-compatible) ports

Three/four synchronous serial ports

Eight 32-bit GP timers, three capture timing units

Four encoder interfaces, 2 with frequency division

One TWI unit, fully compatible with I2C bus standard

Lightweight security

Up to 240 MHz ARM Cortex-M4 with floating-point unit

24-channel analog front end (AFE) with 16-bit ADCs

128K Byte to 384K Byte zero-wait-state L1 SRAM with

16K Byte L1 cache

Up to 2M Byte flash memory

Single 3.3 V power supply

Package Options:

176-lead (24 mm × 24 mm) LQFP package

120-lead (14 mm × 14 mm) LQFP package

212-ball (19 mm × 19 mm) BGA package

Static memory controller (SMC) with asynchronous memory

interface that supports 8-bit and 16-bit memories

Enhanced PWM units

Four 3rd/4th order SINC filter pairs for glueless connection of

sigma-delta modulators

Hardware-based harmonic analysis engine

10/100 Ethernet MAC with IEEE 1588v2 support

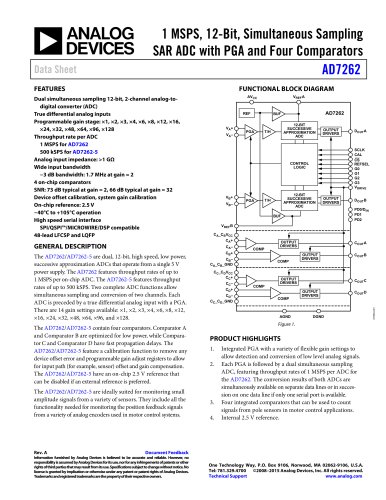

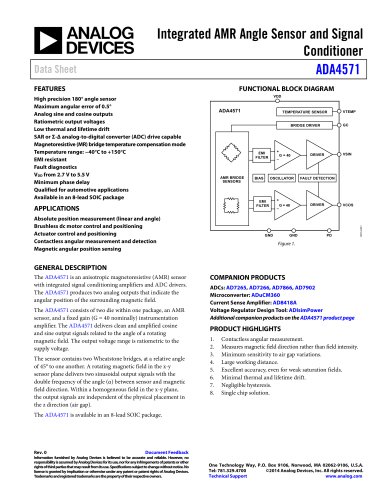

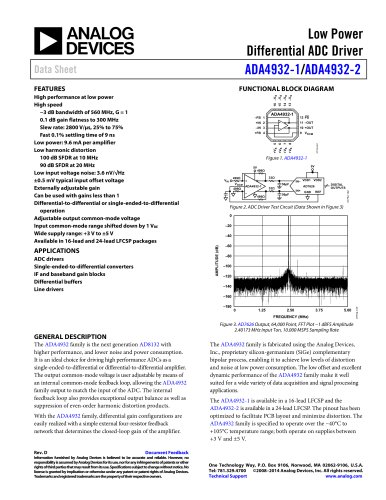

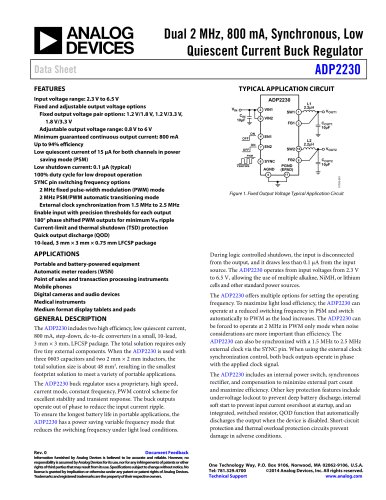

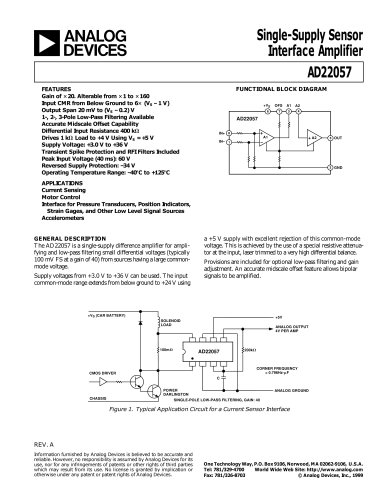

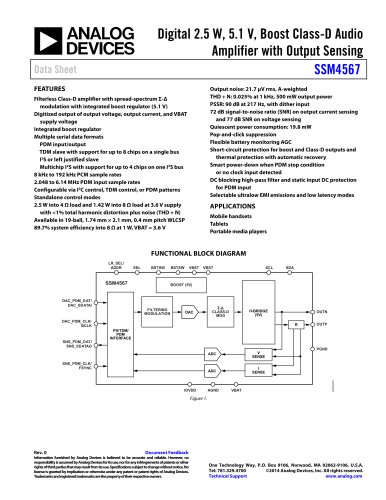

ANALOG FRONT END

Two 16-bit SAR ADCs with up to 24 multiplexed inputs,

supporting dual simultaneous conversion in 380 ns (16-bit,

no missing codes)

ADC controller (ADCC) and DAC controller (DACC)

Two 12-bit DACs

Two 2.5 V precision voltage reference outputs

(For details, see ADC/DAC Specifications on Page 68)

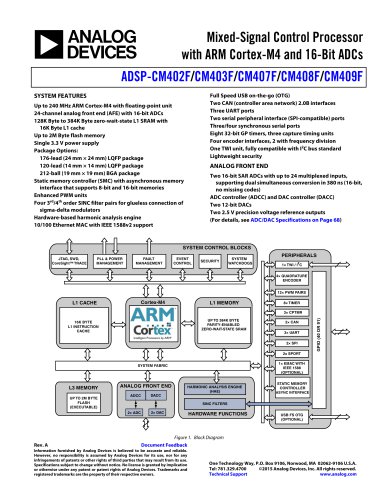

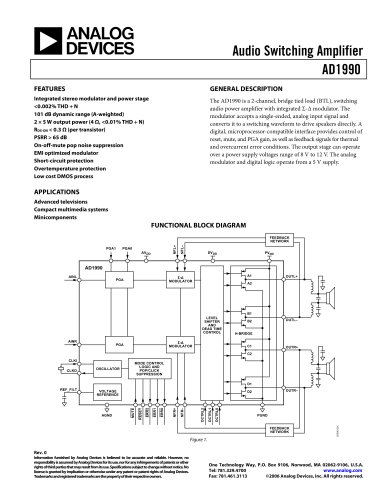

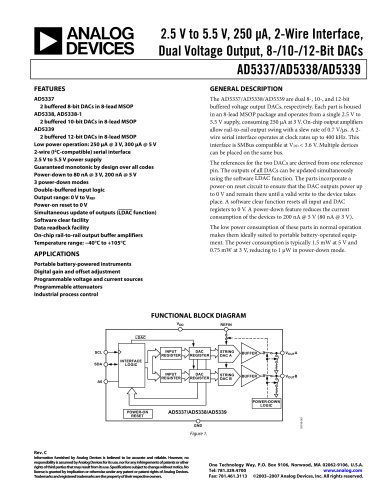

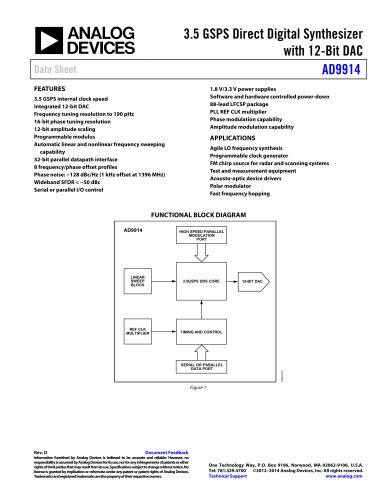

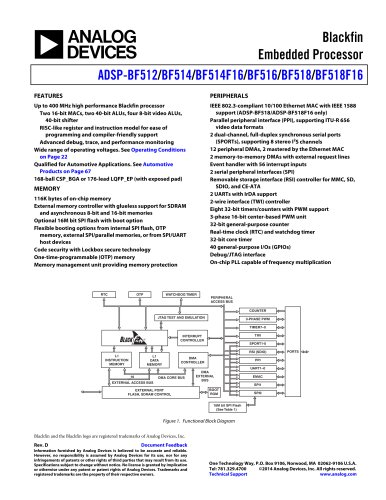

SYSTEM CONTROL BLOCKS

JTAG, SWD,

CoreSight™ TRACE

PLL & POWER

MANAGEMENT

FAULT

MANAGEMENT

EVENT

CONTROL

SECURITY

SYSTEM

WATCHDOGS

PERIPHERALS

2

1× TWI / I C

4× QUADRATURE

ENCODER

12× PWM PAIRS

L1 CACHE

Cortex-M4

L1 MEMORY

8× TIMER

16K BYTE

L1 INSTRUCTION

CACHE

2× CAN

3× UART

2× SPI

GPIO (40 OR 91)

3× CPTMR

UP TO 384K BYTE

PARITY-ENABLED

ZERO-WAIT-STATE SRAM

2x SPORT

1× EMAC WITH

IEEE 1588

(OPTIONAL)

SYSTEM FABRIC

L3 MEMORY

UP TO 2M BYTE

FLASH

(EXECUTABLE)

ANALOG FRONT END

ADCC

DACC

STATIC MEMORY

CONTROLLER

ASYNC INTERFACE

SINC FILTERS

2× ADC

Rev. A

HARMONIC ANALYSIS ENGINE

(HAE)

2× DAC

HARDWARE FUNCTIONS

USB FS OTG

(OPTIONAL)

Figure 1. Block Diagram

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 U.S.A.

Tel: 781.329.4700

©2015 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید