Cyclone V SoC Qseven SOM0 pages

IWave

Embedding Intelligence

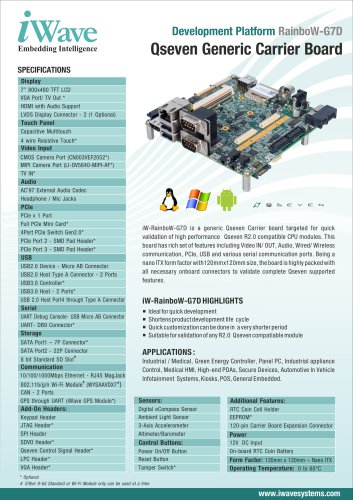

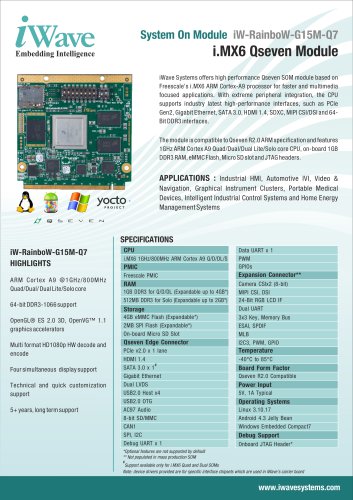

System On Module iW-RainboW-G17M-Q7

Cyclone V SoC Qseven Module

17

iW-RainboW-G17M-Q7

HIGHLIGHTS

ARM Cortex A9 Dual core CPU

integrated with FPGA with up to 110K

LEs

Enhanced with integrated transceivers

and hard memory controller

Readily available FPGA IP cores for

integration

R2.0 Qseven compatible module

iWave Systems launched world's first Altera Cyclone V SX SoC FPGA based Qseven

compatible module for the increased system performance requirements. The dual ARM

Cortex A9 core with the FPGA allows greater flexibility for the system designers and helps

to lower the system cost and power consumption. The improved logic integration with

integrated high speed transceivers and hard memory controllers provides increased

bandwidth capacity which is ideal for cost-sensitive high end applications.

APPLICATIONS: Industrial Automation, Smart Energy Systems, Video

Surveillance, Defenses Aerospace

SPECIFICATIONS

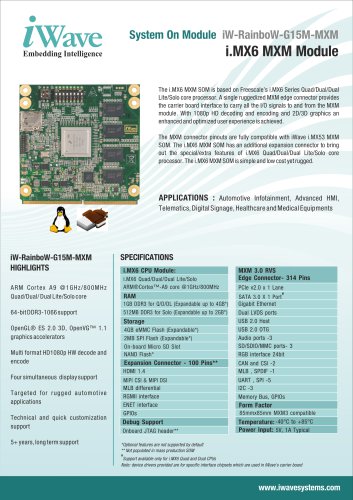

CPU: | Qseven PCB Edge Connector Interfaces: |

Altera's Cyclone V SX SoC FPGA | From HPS: |

• Integrated Dual core ARM Cortex-A9 | Gigabit Ethernet - 1 Port (On-SOM PHY) |

Hard Processor System(HPS) | USB 2.0 Host - 4 Ports (On-SOM HUB) |

• FPGA with upto 11 OK LEs | CAN - 1 Port |

Memory: | SD/MMC (8 bit)* |

512MB DDR3 with ECC for HPS | WDOG - 1 Port |

16MB QSPI Flash* | I2C - 2 Ports |

On-SOM Micro SD Connector* | SPI - 1 Port |

256MB DDR3 for FPGA | Debug UART - 1 Port |

EPCQ Flash/QSPI Flash for FPGA* | 2nd UART - 1 Port |

EEPROM* | Other Control IOs - Through HPS |

On Board Peripherals Support: | From FPGA+: |

JTAG Header for FPGA | LVDS LCD - 2 Ports (FPGA Soft IP)/23 SE IOs |

JTAG Header for HPS* | AC97/I2S Audio (FPGA Soft IP)/5 SE IOs |

DIP Switch for boot settings | PWM |

RTC controller | FPGA IOs - 8 SE IOs |

From FPGA High Speed Transceivers : | |

FPGA IOs (Up to 45 Single Ended 10s - SE 10s) | PCIe Gen1 x 4 Lane |

9 TX LVDS Pairs/18 SE IOs | SATA (FPGA Soft IP) |

11 RX LVDS Pairs/22 SE IOs | Form Factor: |

5 Single Ended IOs | 70mm x 70mm Qseven Specification 2.0 |

FPGA Dedicated Clock IOs: | Power Input: |

General Purpose Clock Inputs (2 LVDS/2 SE) | 5V DC |

General Purpose Clock Outputs (1 LVDS/2 SE) | Operating Temperature: |

Others: | -40°C to +85°C Industrial |

SMBUS/2 SE IOs | Operating System: |

FPGA JTAG | Linux 3.10 |

On-SOM Micro SD Connector and Qseven Edge SD/MMC are sharing the same interface

* If the FPGA interfaces available in the Qseven edge are not used for Qseven compliance requirement, same interface

pins can be used for custom Industrial/networking interface requirements._

www.iwavesystems.com

"

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید