64M x 8, 32M x 16 512Mb SYNCHRONOUS DRAM0 pages

IS42S86400B

IS42S16320B, IS45S16320B

Integrated Silicon Solution, Inc. — www.issi.com 1

Rev. F

12/14/2010

Copyright © 2010 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without

notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain

the latest version of this device specification before relying on any published information and before placing orders for products.

Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can

reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications

unless Integrated Silicon Solution, Inc. receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

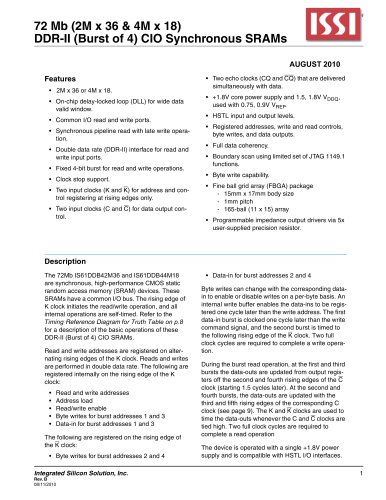

FEATURES

• Clock frequency: 166, 143, 133 MHz

• Fully synchronous; all signals referenced to a

positive clock edge

• Internal bank for hiding row access/precharge

• Power supply

Vdd Vddq

IS42/45S16320B 3.3V 3.3V

IS42S86400B 3.3V 3.3V

• LVTTL interface

• Programmable burst length

– (1, 2, 4, 8, full page)

• Programmable burst sequence:

Sequential/Interleave

• Auto Refresh (CBR)

• Self Refresh

• 8K refresh cycles every 16ms (A2 grade) or

64 ms (Commercial, Industrial, A1 grade)

• Random column address every clock cycle

• Programmable CAS latency (2, 3 clocks)

• Burst read/write and burst read/single write

operations capability

• Burst termination by burst stop and precharge

command

• Available in 54-pin TSOP-II and 54-ball W-BGA

(x16 only)

• Operating Temperature Range:

Commercial: 0oC to +70oC

Industrial: -40oC to +85oC

Automotive, A1: -40oC to +85oC

Automotive, A2: -40oC to +105oC

OVERVIEW

ISSI's 512Mb Synchronous DRAM achieves high-speed

data transfer using pipeline architecture. All inputs and

outputs signals refer to the rising edge of the clock input.

The 512Mb SDRAM is organized as follows.

64M x 8, 32M x 16

512Mb SYNCHRONOUS DRAM DECEMBER 2010

KEY TIMING PARAMETERS

Parameter -6 -7 -75E Unit

Clk Cycle Time

CAS Latency = 3 6 7 – ns

CAS Latency = 2 10 10 7.5 ns

Clk Frequency

CAS Latency = 3 166 143 – Mhz

CAS Latency = 2 100 100 133 Mhz

Access Time from Clock

CAS Latency = 3 5.4 5.4 – ns

CAS Latency = 2 6 6 5.5 ns

IS42S86400B IS42/45S16320B

16Mx8x4 Banks 8M x16x4 Banks

54-pin TSOPII 54-pin TSOPII

54-ball W-BGA

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید