X-ray data acquisition high energy XDAS-HE0 pages

X-ray data acquisition high energy

XDAS-HE

1

SENS-TECH

SENSOR TECHNOLOGIES

description

XDAS-HE is a modular system of boards for data acquisition

in linescan systems using X-ray or Linac sources. The large

dynamic range of the detector makes it possible to use high

energies and pulsed sources. An XDAS-HE system consists

of a set of detector head boards and signal processing

boards. Each detector head board has 64 detector channels.

Up to 7 signal processing boards can be used in a single

system, each driving 64 detector head boards. This data

sheet describes the 2.5mm pitch system but other

configurations, with adapter boards, can be supplied to

special order.

2 applications

·

container inspection

·

vehicle checking

·

cargo inspection

3

features

·

modular system with up to 64 detector head boards per

signal processing board

· mm detector pitch, other designs to special order

2.5

· electronic noise

low

·

range of scintillator types

·

simultaneous data acquisition and read-out

· dynamic range 50pC to 350 pC

wide

· bit output

20

· µs minimum signal integration time

320

·

energy up to 6MeV

4

XDAS-HE system

Current from the photodiodes is integrated by a microcircuit

containing 64 charge sensitive amplifiers and a 20-bit A/D

convertor. The microcircuit provides a serial digital output

which is fed to the signal processing board using LVDS

transceivers.

Operation is continuous, with one set of data being read-out

whilst the next set is acquired. Dead time is less than 100ns.

There is zero dead time in continuous scan mode. In

triggered mode, dead-time depends on system configuration.

Contact Sens-Tech for advice.

The maximum charge that can be collected per cycle

depends on the choice of storage capacitors, one per

channel, which are internal to the microcircuit. These can be

set from 50pC to 350pC in steps of 50pC. High linearity is

maintained with charge storage of 50pC to 350pC per cycle.

Each detector board may be programmed with a different

charge capacity.

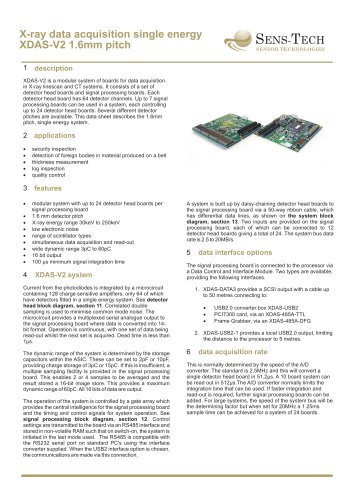

A system is built up by daisy-chaining detector head boards to

the signal processing board via a 50-way ribbon cable, which

has differential data lines, as shown on detector head block

diagram, Section 11. Four inputs are provided on the signal

processing board, each of which can be connected to 16

detector head boards giving a total of 64 detector head

boards for one signal processing board. There can be up to 7

signal processing boards in a system.

The operation of the system is controlled by a gate array

(FPGA), which provides the central intelligence for the board

and the timing and control signals for system operation. See

system block diagram, Section 12.

User settings to control integration times, sub-sampling and

refresh rate, together with information on system

configuration, are transmitted via an LVDS interface and

stored in non-volatile RAM such that on switch-on, the system

is initiated in the last mode used. The LVDS is compatible

with the RS232 serial port on standard PC's using the

interface converter supplied. When the USB2 or Ethernet

option is chosen, the communications are made via this

connection.

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید