AD9680: 14-Bit, 1 GSPS JESD204B, Dual Analog-to-Digital Converter0 pages

14-Bit, 1 GSPS JESD204B,

Dual Analog-to-Digital Converter

AD9680

Data Sheet

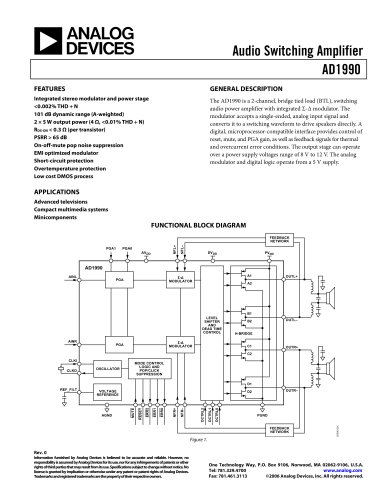

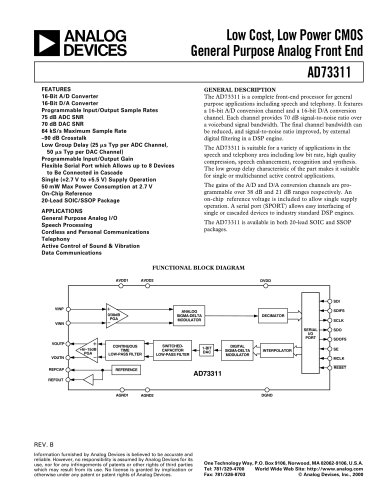

FEATURES

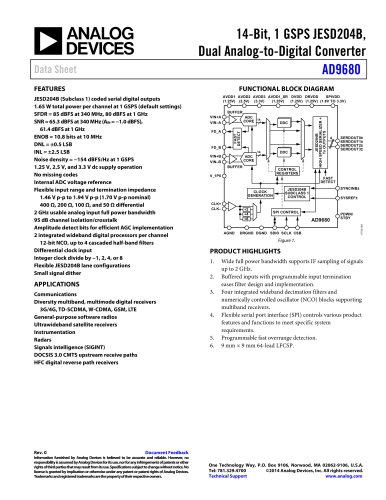

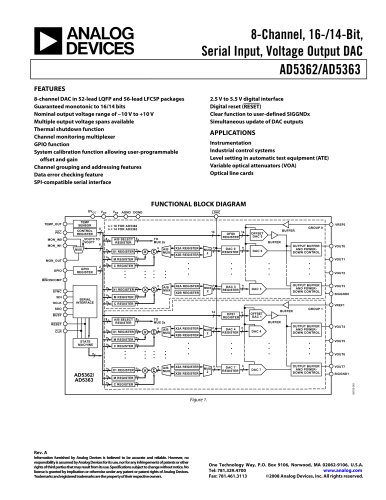

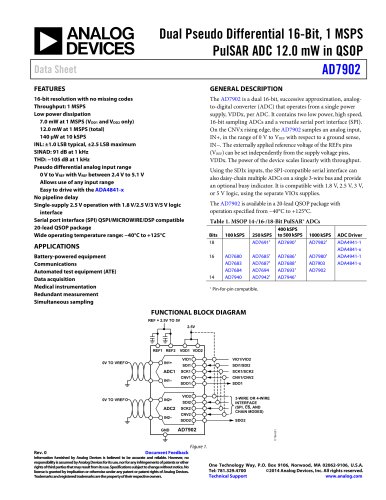

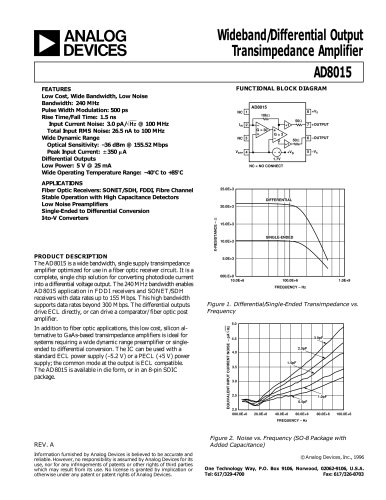

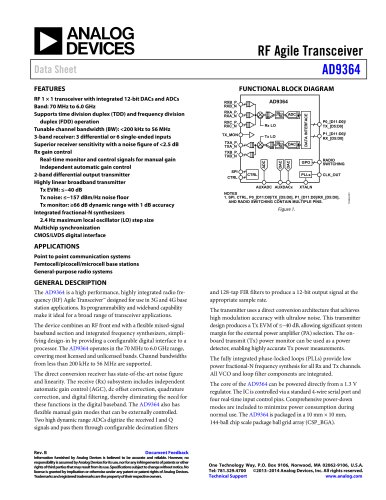

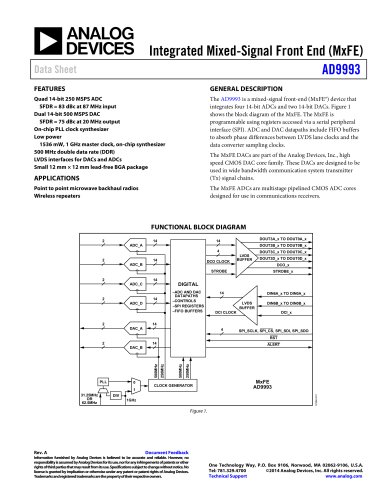

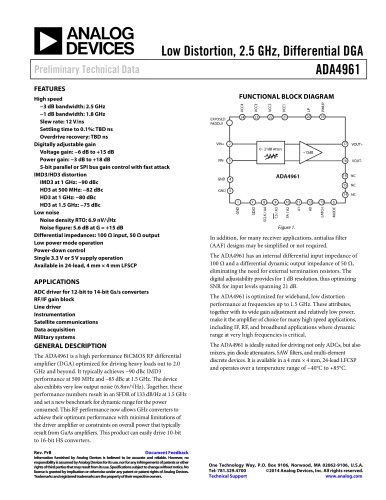

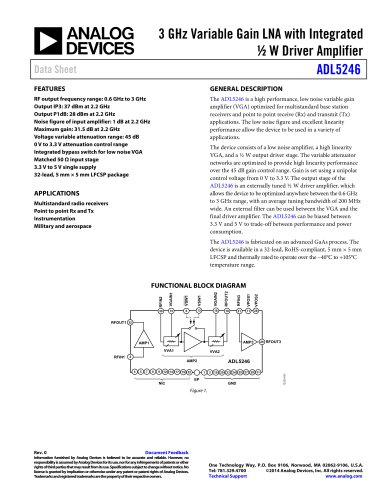

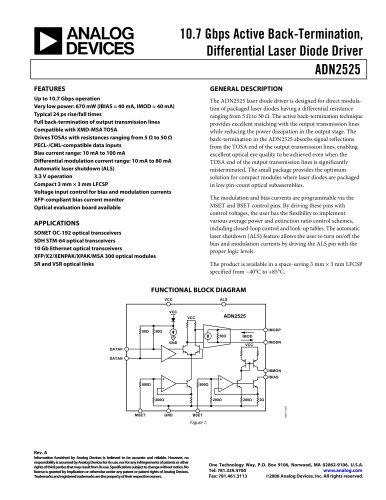

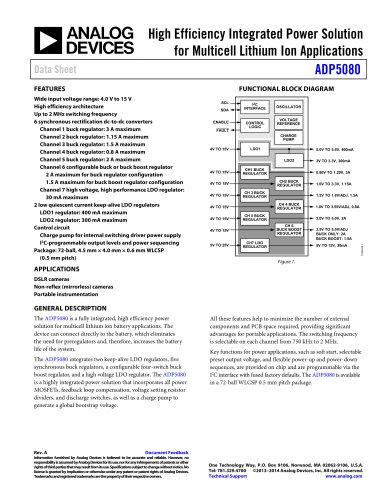

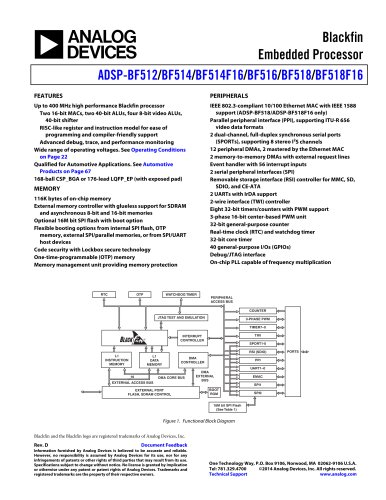

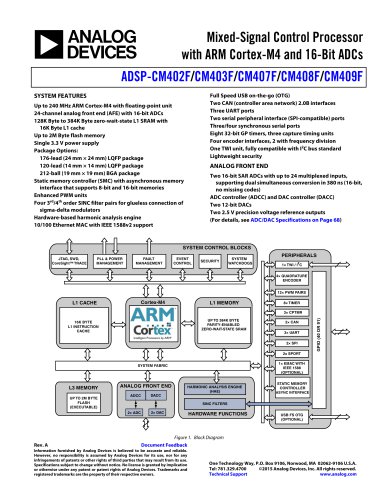

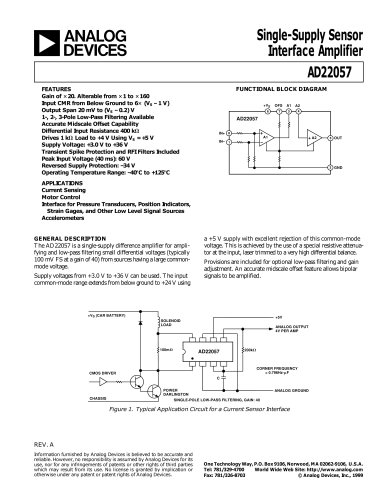

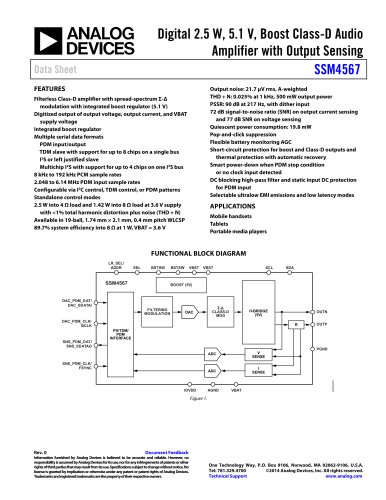

FUNCTIONAL BLOCK DIAGRAM

AVDD1 AVDD2 AVDD3 AVDD1_SR DVDD DRVDD

SPIVDD

(1.25V) (2.5V) (3.3V)

(1.25V)

(1.25V) (1.25V) (1.8V TO 3.3V)

FD_B

14

VIN+B

VIN–B

Rev. 0

DDC

ADC

CORE

BUFFER

4

SERDOUT0±

SERDOUT1±

SERDOUT2±

SERDOUT3±

CONTROL

REGISTERS

V_1P0

FAST

DETECT

CLK+

CLK–

÷2

÷4

÷8

AGND

SYNCINB±

JESD204B

SUBCLASS 1

CONTROL

CLOCK

GENERATION

SYSREF±

SPI CONTROL

AD9680

DRGND DGND SDIO SCLK CSB

PDWN/

STBY

Figure 1.

PRODUCT HIGHLIGHTS

1.

2.

APPLICATIONS

Communications

Diversity multiband, multimode digital receivers

3G/4G, TD-SCDMA, W-CDMA, GSM, LTE

General-purpose software radios

Ultrawideband satellite receivers

Instrumentation

Radars

Signals intelligence (SIGINT)

DOCSIS 3.0 CMTS upstream receive paths

HFC digital reverse path receivers

DDC

11752-001

FD_A

ADC

CORE 14

JESD204B

HIGH SPEED SERIALIZER +

Tx OUTPUTS

BUFFER

VIN+A

VIN–A

FAST

DETECT

JESD204B (Subclass 1) coded serial digital outputs

1.65 W total power per channel at 1 GSPS (default settings)

SFDR = 85 dBFS at 340 MHz, 80 dBFS at 1 GHz

SNR = 65.3 dBFS at 340 MHz (AIN = −1.0 dBFS),

61.4 dBFS at 1 GHz

ENOB = 10.8 bits at 10 MHz

DNL = ±0.5 LSB

INL = ±2.5 LSB

Noise density = −154 dBFS/Hz at 1 GSPS

1.25 V, 2.5 V, and 3.3 V dc supply operation

No missing codes

Internal ADC voltage reference

Flexible input range and termination impedance

1.46 V p-p to 1.94 V p-p (1.70 V p-p nominal)

400 Ω, 200 Ω, 100 Ω, and 50 Ω differential

2 GHz usable analog input full power bandwidth

95 dB channel isolation/crosstalk

Amplitude detect bits for efficient AGC implementation

2 integrated wideband digital processors per channel

12-bit NCO, up to 4 cascaded half-band filters

Differential clock input

Integer clock divide by −1, 2, 4, or 8

Flexible JESD204B lane configurations

Small signal dither

3.

4.

5.

6.

Wide full power bandwidth supports IF sampling of signals

up to 2 GHz.

Buffered inputs with programmable input termination

eases filter design and implementation.

Four integrated wideband decimation filters and

numerically controlled oscillator (NCO) blocks supporting

multiband receivers.

Flexible serial port interface (SPI) controls various product

features and functions to meet specific system

requirements.

Programmable fast overrange detection.

9 mm × 9 mm 64-lead LFCSP.

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

©2014 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

عضویت

عضویت  ورود اعضا

ورود اعضا راهنمای خرید

راهنمای خرید